# **SERIES - 100 FLASH MEMORY CARD**

16MB/8MB/4MB

**Product Specification**

# **Documentation History**

| Version | Description | Date      | Written By   |

|---------|-------------|-----------|--------------|

| 0       | New issued  | Feb. 2001 | Roger K. Hsi |

## **Contents**

| FEATURES / GENERAL DESCRIPTION                              |  |

|-------------------------------------------------------------|--|

| PRODUCT NUMBER DEFINITION                                   |  |

| BLOCK DIAGRAM3                                              |  |

| PIN CONFIGURATION (16MB CARD)4                              |  |

| PIN DESCRIPTION4                                            |  |

| PIN LOCATION5                                               |  |

| RECOMMENDED OPERATING CONDITIONS5                           |  |

| ABSOLUTE MAXIMUM RATING *                                   |  |

| FUNCTION TABLE6                                             |  |

| CARD INFORMATION STRUCTURE7                                 |  |

| CIS DATA                                                    |  |

| COMMAND SET TABLE                                           |  |

| COMMAND DEFINITIONS                                         |  |

| READ ARRAY COMMAND11                                        |  |

| READ IDENTIFIER CODES COMMAND11                             |  |

| READ STATUS REGISTER COMMAND11                              |  |

| CLEAR STATUS REGISTER COMMAND12                             |  |

| BLOCK ERASE COMMAND                                         |  |

| BLOCK ERASE SUSPEND/BLOCK ERASE RESUME COMMANDS             |  |

| PROGRAM COMMAND13                                           |  |

| PROGRAM SUSPEND/PROGRAM RESUME COMMANDS14                   |  |

| SET BLOCK LOCK-BIT COMMAND , CLEAR BLOCK LOCK-BIT COMMAND14 |  |

| DEVICE STATUS REGISTER DEFINITION                           |  |

| DEVICE LEVEL AUTOMATED PROGRAM ALGORITHM 16                 |  |

## C-ONE

## **SERIES-100 FLASH MEMORY CARD**

| DEVICELEVEL AUTOMATED BLOCK ERASE ALGORITHM      |

|--------------------------------------------------|

| DEVICELEVEL PROGRAM SUSPEND/RESUME ALGORITHM     |

| DEVICELEVEL BLOCK ERASE SUSPEND/RESUME ALGORITHM |

| DEVICELEVEL SET BLOCK LOCK-BIT ALGORITHM         |

| DEVICELEVEL CLEAR BLOCK LOCK-BIT ALGORITHM       |

| DC ELECTRICAL CHARACTERISTICS                    |

| AC ELECTRICAL CHARACTERISTICS                    |

| READ CYCLE                                       |

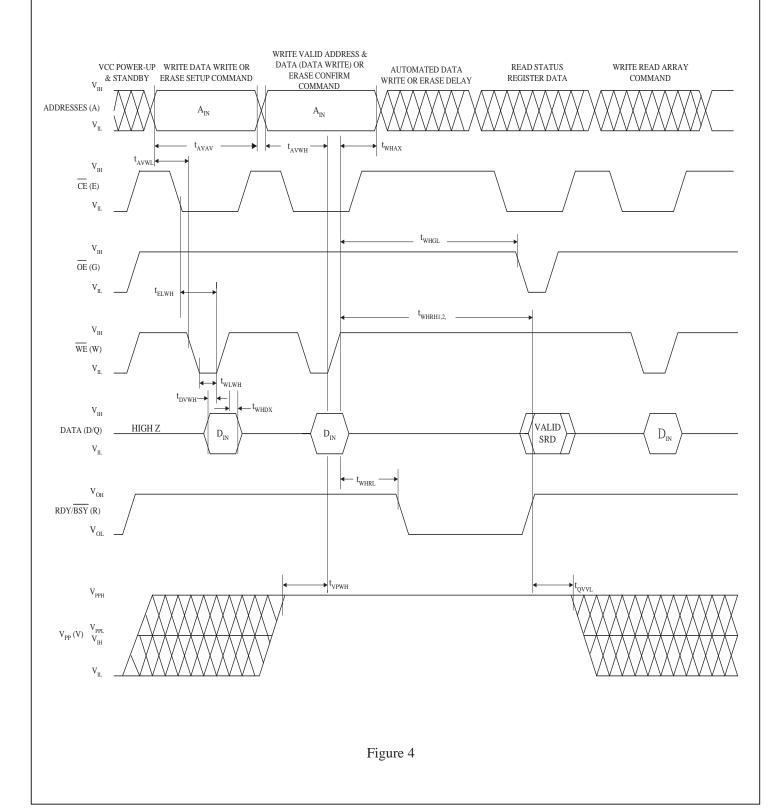

| WRITE CYCLE                                      |

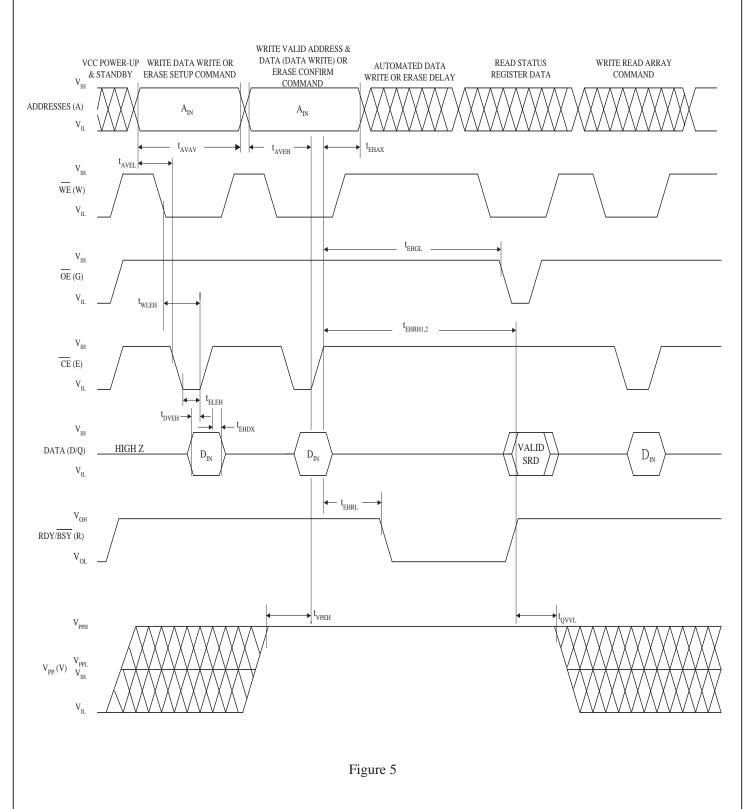

| WRITE CYCLE (CE* CONTROLLED)                     |

| READ CYCLE TIMING DIAGRAM                        |

| WRITE CYCLE TIMING DIAGRAM                       |

| WRITE CYCLE TIMING DIAGRAM (CE* CONTROLLED)      |

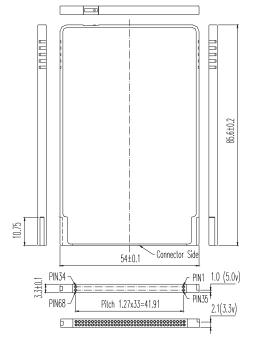

| OUTLINE DIMENSIONS (UNIT: MM)                    |

#### **Features**

★ PC Card Standard Type 1 form factor

★ Low cost, word(x16) only data bus

★ Memory Capacity: 4MB/8MB/16MB

★ Single power: 5V Vcc or dual power: 5V Vcc , 5/12V Vpp ★ Enhanced automated suspend capability

★ Read voltage: 5V, program/erase voltage: 5V or 12V

★ Fast read access time: 200ns (maximum)

★ Fast word random program : 6us (typ.) @ Vpp = 12V

8us (typ.) @ Vpp = 5V

★ 64K words per block structure

★ 100000 program/erase cycles per block

★ Fast block erase time : 1 sec (typical) @ Vpp = 12V

1.1 sec (typical) @ Vpp = 5V

★ Automatic erase/write

- command user interface

- status register

- program suspend to read

- block erase suspend to program

- block erase suspend to read

★ Enhanced data protection feature

- flexible block locking

★ Built-in write protect switch

★ Commercial / Industrial grade

## **General Description**

C-ONE's SERIES-100 Flash memory card family conforms to the PCMCIA / JEIDA international standard but with word (16 bit) operation only. Without the complicated control logic circuit and attribute memory design, it is the lowcost version of the C-ONE's SMART 5 Flash memory card family. With the flexible power supply design in this card family, user can choose single 5V Vcc or dual power supply (Vcc and Vpp). Choosing the dual power supply, user can also choose 5V or 12V as the Vpp supply voltage flexibly.

Like the SMART 5 Flash memory card family consisting of multiple Intel's 28F008S5 (or 28F016S5), this card family also maintains backwards-compatibility with the C-ONE's SERIES 2 Flash memory card family which consist of Intel's 28F008SA Flash memory devices. Key enhancements include: 1) smart voltage allows Vpp to be 5V or 12V, 12V option renders the faster block erase, program performance. 2) enhanced suspend capabilities. 3) in-system block locking.

This series Flash memory cards contain 16, 32, 64 or 128 independent 64K-word blocks. Each block can be individually erasable. To reduce the attribute memory cost overhead, the Card Information Structure (CIS) is stored in Block 0 of the flash memory array. In embedded applications, the CIS may not be required by the system and the entire flash memory array can be used by the system.

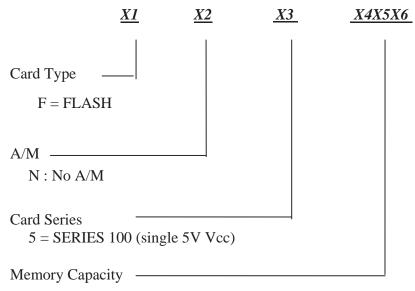

#### **Product Number Definition**

004 : 4MB 008 : 8MB 016 : 16MB

Note: A/M means attribute memory.

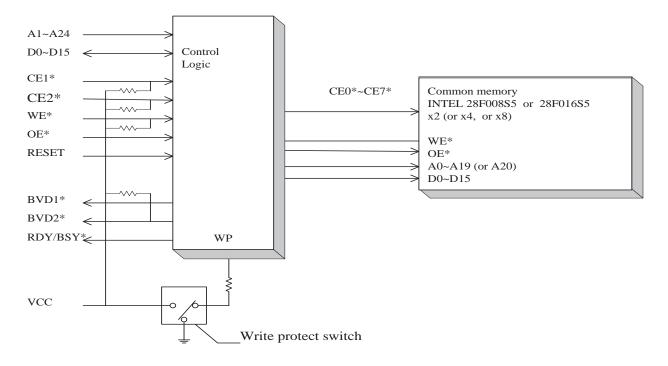

## Block Diagram

Figure 1

## Pin Configuration (16MB card)

| 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | Pin no.  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----------|

| V  | R  | W  | A  | A  | A  | A  | A  | О  | A  | С  | D  | D  | D  | D  | D  | G  | Pin Name |

| С  | Y  | Е  | 1  | 1  | 8  | 9  | 1  | Е  | 1  | E  | 7  | 6  | 5  | 4  | 3  | N  |          |

| С  | /  | *  | 4  | 3  |    |    | 1  | *  | 0  | 1  |    |    |    |    |    | D  |          |

|    | В  |    |    |    |    |    |    |    |    | *  |    |    |    |    |    |    |          |

|    | Y  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |          |

|    | *  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |          |

| 34 | 33 | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | Pin No.  |

| G  | W  | D  | D  | D  | N  | A  | A  | A  | A  | A  | A  | A  | A  | A  | A  | V  | Pin Name |

| N  | P  | 2  | 1  | 0  | C  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 1  | 1  | 1  | P  |          |

| D  |    |    |    |    |    |    |    |    |    |    |    |    | 2  | 5  | 6  | P  |          |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  |          |

| 51 | 50 | 49 | 48 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | Pin No.  |

| V  | Α  | A  | Α  | Α  | A  | N  | N  | N  | C  | D  | D  | D  | D  | D  | С  | G  | Pin Name |

| С  | 2  | 2  | 1  | 1  | 1  | C  | C  | C  | Е  | 1  | 1  | 1  | 1  | 1  | D  | N  |          |

| С  | 1  | 0  | 9  | 8  | 7  |    |    |    | 2  | 5  | 4  | 3  | 2  | 1  | 1  | D  |          |

|    |    |    |    |    |    |    |    |    | *  |    |    |    |    |    | *  |    |          |

| 68 | 67 | 66 | 65 | 64 | 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54 | 53 | 52 | Pin No.  |

| G  | С  | D  | D  | D  | В  | В  | N  | N  | N  | R  | N  | N  | A  | A  | A  | V  | Pin Name |

| N  | D  | 1  | 9  | 8  | V  | V  | С  | С  | C  | E  | С  | С  | 2  | 2  | 2  | P  |          |

| D  | 2  | 0  |    |    | D  | D  |    |    |    | S  |    |    | 4  | 3  | 2  | P  |          |

|    | *  |    |    |    | 1  | 2  |    |    |    | Е  |    |    |    |    |    | 2  |          |

|    |    |    |    |    | *  | *  |    |    |    | T  |    |    |    |    |    |    |          |

Table 2

**Note**: \*mean low active

2MB card : A22, A23, A24 = NC 4MB card : A23, A24 = NC 8MB card : A24 = NC

For single 5V Vcc cards, Vpp1 (pin no. 18) and Vpp2 (pin no. 52) are NC

## Pin Description

| Symbol      | Function                                             | I/O |

|-------------|------------------------------------------------------|-----|

| A1-A24      | Addresses                                            | I   |

| D0-D15      | Data Inputs/Outputs                                  | I/O |

| CE1*/CE2*   | Card Enable                                          | I   |

| OE*         | Output Enable                                        | I   |

| WE*         | Write Enable                                         | I   |

| RESET       | Card Reset                                           | I   |

| WP          | Write-protect status Detect                          | О   |

| BVD1*/BVD2* | Battery Voltage Detect (pull high to Vcc internally) | О   |

| RY/BY*      | Ready/Busy status                                    | О   |

| CD1*/CD2*   | Card Detect (tied to GND internally)                 | О   |

| VCC         | +5 Volt Power Supply                                 | -   |

| VPP1/VPP2   | Write (programming) Power Supply                     | -   |

| GND         | Ground                                               |     |

| NC          | No Connection                                        | -   |

Table 3

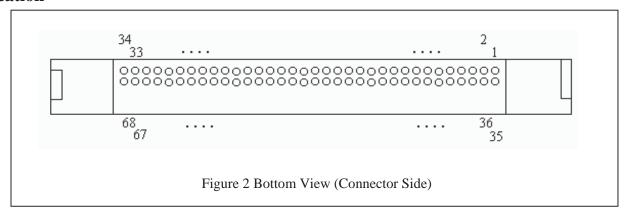

#### **Pin Location**

## **Recommended Operating Conditions**

| Parameter                                      | Symbol                                | Min.     | Max.      | Unit |

|------------------------------------------------|---------------------------------------|----------|-----------|------|

| V <sub>CC</sub> Supply Voltage                 | $V_{CC}$                              | 4.5      | 5.5       | V    |

| V <sub>PP</sub> Supply Voltage (read)          | $V_{\mathrm{PPL}}$                    | 0        | 6.5       | V    |

| V <sub>PP</sub> Supply Voltage (erase/program) | V <sub>PPH1</sub> / V <sub>PPH2</sub> | 4.5/11.4 | 5.5/12.6  | V    |

| Input High Voltage                             | $V_{\mathrm{IH}}$                     | 2.4      | VCC + 0.3 | V    |

| Input Low Voltage                              | $V_{\mathrm{IL}}$                     | -0.3     | 0.8       | V    |

| Operating Temperature(Commercial)              | $T_{OPR}$                             | 0        | 70        | ° C  |

| Operating Temperature(Industrial)              | $T_{OPR}$                             | -40      | 85        | ° C  |

Table 4

## **Absolute Maximum Rating \***

| Parameter                                    | Symbol             | Value                                          | Unit |

|----------------------------------------------|--------------------|------------------------------------------------|------|

| V <sub>CC</sub> Supply Voltage               | $V_{CC}$           | -0.5 to +6.0                                   | V    |

| V <sub>PP</sub> Supply Voltage (read)        | $V_{\mathrm{PPL}}$ | -2.0 to +7.0                                   | V    |

| V <sub>PP</sub> Supply Voltage (erase/write) | $V_{\mathrm{PPH}}$ | -2.0 to +14.0                                  | V    |

| Input Voltage                                | V <sub>IN</sub>    | $-0.5 \text{ to V}_{CC} + 0.3(6\text{V max.})$ | V    |

| Output Voltage                               | V <sub>OUT</sub>   | -0.5 to +6.0                                   | V    |

| Operating Temperature (Commercial)           | $T_{OPR}$          | 0 to +70                                       | ° C  |

| Operating Temperature (Industrial)           | $T_{OPR}$          | -40 to +85                                     | ° C  |

| Storage Temperature                          | $T_{STR}$          | -40 to +125                                    | ° C  |

| Relative Humidity (non-condensing)           | $H_{UM}$           | 95(maximum)                                    | %    |

Table 5

#### \*Comments

Stress above those listed under " Absolute Maximum Ratings " may cause permanent damage to the products. These are stress rating only. Functional operation of these products at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Function Table**

| Function        | RESET | CE2* | CE1* | A1 | OE* | WE* | $V_{PP1/2}$     | D15-D8   | D7-D0     |

|-----------------|-------|------|------|----|-----|-----|-----------------|----------|-----------|

| Standby         | L     | Н    | Н    | X  | X   | X   | $V_{	ext{PPL}}$ | High-Z   | High-Z    |

| Even Byte Read  | L     | Н    | L    | X  | L   | Н   | $V_{	ext{PPL}}$ | High-Z   | Even Byte |

| Odd Byte Read   | L     | L    | Н    | X  | L   | Н   | $V_{	ext{PPL}}$ | Odd Byte | High-Z    |

| Word Read       | L     | L    | L    | X  | L   | Н   | $V_{	ext{PPL}}$ | Odd Byte | Even Byte |

| Even Byte Write | L     | Н    | L    | X  | Н   | L   | $V_{PPH}$       | X        | Even Byte |

| Odd Byte Write  | L     | L    | Н    | X  | Н   | L   | $V_{PPH}$       | Odd Byte | X         |

| Word Write      | L     | L    | L    | X  | Н   | L   | $V_{PPH}$       | Odd Byte | Even Byte |

| Manufacturer ID | L     | L    | L    | L  | L   | Н   | $V_{	ext{PPL}}$ | 89H      | 89H       |

| Device ID       | L     | L    | L    | Н  | L   | Н   | $V_{	ext{PPL}}$ | A6H (or  | A6H (or   |

|                 |       |      |      |    |     |     |                 | AAH)     | AAH)      |

| Output Disable  | L     | X    | X    | X  | Н   | Н   | $V_{	ext{PPL}}$ | High-Z   | High-Z    |

| Power Down      | Н     | X    | X    | X  | X   | X   | $V_{PPH}$       | High-Z   | High-Z    |

Table 6

#### Notes:

- 1.  $L=V_{IL}$  ;  $H=V_{IH}$  ;  $X=\mbox{don't care}$  , can be either  $V_{IH}$  or  $V_{IL}.$

- 2. VPPH can be either VPPH1 (4.5V to 5.5V) or VPPH2 (11.4V to 12.6V).

#### **Card Information Structure**

The Series-100 flash memory card does not implement a separate memory plane for the attribute memory space. The Card Information Structure (CIS) is stored in the Block 0 (first 64K-word block) starting from address zero of the card's common memory plane and resides sequentially in memory locations with even memory addresses. It contains a variable-length chain of data blocks (tuples) which conform to the basic format defined in PC Card Standard. The Series-100 flash memory card tuple contains a Long Link Tuple which will point to Block pair 1 in common memory (20000 Hex) after the tuples have been parsed. The generic CIS of C-ONE'S Series-100 flash memory card is shown in table 7.

**Note :** If the tuples are needed by the host system to identify the Series-100 flash memory card, the system software **can not** use Block pair 0 in common memory (00000 Hex ~ 1FFFF Hex). Many flash card formatters available will erase Block pair 0 if the card is reformatted.

For some embedded and PC applications, the host system may not need the tuples to determine the type of flash memory devices used and the card's density, the system can identify the flash devices in the card by using the Read Identify Codes command. Under such situations, there will be no CIS stored in the Block 0, user can use the entire common memory plane without restriction.

SERIES100FLADS0 6/23 0102V0

| C-ONE    | SERIES-100 FLASH MEMORY CARD                             |

|----------|----------------------------------------------------------|

| CIS Data |                                                          |

| Tab.     | le 7 Generic CIS of C-ONE'S Series-100 flash memory card |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

## C-ONE

## **SERIES-100 FLASH MEMORY CARD**

| Tuple Address<br>(Hex) | Data<br>(Hex) | Description               |

|------------------------|---------------|---------------------------|

| 00                     | 01            | CISTPL_DEVICE             |

| 02                     | 03            | TPL_LINK                  |

| 04                     | 52            | DEVICE_INFO = FLASH 200ns |

| 06                     | 06            | CARD SIZE 2MB             |

|                        | 0E            | 4MB                       |

|                        | 1E            | 8MB                       |

|                        | 3E            | 16MB                      |

| 08                     | FF            | CISTPL_END                |

| 0A                     | 15            | CISTPL_VERS_1             |

| 0C                     | 20            | TPL_LINK                  |

| 0E                     | 05            | TPLLV1_MAJOR              |

| 10                     | 00            | TPLLV1_MINOR              |

| 12                     | 53            | S                         |

| 14                     | 45            | Е                         |

| 16                     | 52            | R                         |

| 18                     | 49            | I                         |

| 1A                     | 45            | Е                         |

| 1C                     | 53            | S                         |

| 1E                     | 2D            | -                         |

| Tuple Address (Hex) | Data<br>(Hex) | Description         |

|---------------------|---------------|---------------------|

| 20                  | 31            | 1                   |

| 22                  | 30            | 0                   |

| 24                  | 30            | 0                   |

| 26                  | 20            | SPACE               |

| 28                  | 20            | SPACE (for 2/4/8MB) |

|                     | 31            | 1 (for 16MB)        |

| 2A                  | 32            | 2                   |

|                     | 34            | 4                   |

|                     | 36            | 6                   |

|                     | 38            | 8                   |

| 2C                  | 4D            | M                   |

| 2E                  | 42            | В                   |

| 30                  | 20            | SPACE               |

| 32                  | 46            | F                   |

| 34                  | 4C            | L                   |

| 36                  | 41            | A                   |

| 38                  | 53            | S                   |

| 3A                  | 48            | Н                   |

| 3C                  | 20            | SPACE               |

| Tuple Address<br>(Hex) | Data<br>(Hex) | Description                            |

|------------------------|---------------|----------------------------------------|

| 3E                     | 43            | С                                      |

| 40                     | 41            | A                                      |

| 42                     | 52            | R                                      |

| 44                     | 44            | D                                      |

| 46                     | 00            | Product Information terminated by NULL |

| 48                     | 00            | No Additional Product<br>Information   |

| 4A                     | 00            | No Additional Product<br>Information   |

| 4C                     | FF            | CISTPL_END                             |

| 4E                     | 18            | CISTPL_JEDEC_C                         |

| 50                     | 02            | TPL_LINK                               |

| 52                     | 89            | INTEL JEDEC ID                         |

| 54                     | A6            | 28F008S5 JEDEC ID                      |

|                        | AA            | 28F016S5 JEDEC ID                      |

| 56                     | 1E            | CISTPL_DEVICEGEO                       |

| 58                     | 06            | TPL_LINK                               |

| 5A                     | 02            | DGTPL_BUS                              |

| 5C                     | 11            | DGTPL_EBS                              |

| 5E                     | 01            | DGTPL_RBS                              |

| 60                     | 01            | DGTPL_WBS                              |

| Tuple Address<br>(Hex) | Data<br>(Hex) | Description                           |

|------------------------|---------------|---------------------------------------|

| 62                     | 03            | DGTPL_PART                            |

| 64                     | 01            | DGTPL_HWIL                            |

| 66                     | 21            | CISTPL_FUNCID                         |

| 68                     | 02            | TPL_LINK                              |

| 6A                     | 01            | MEMORY CARD                           |

| 6C                     | 00            | NO EXPANSION ROM & POWER ON SELF TEST |

| 6E                     | 12            | CISTPL_LONGLINK_C                     |

| 70                     | 04            | TPL_LINK                              |

| 72                     | 00            | LOWEST BYTE                           |

| 74                     | 00            |                                       |

| 76                     | 02            |                                       |

| 78                     | 00            | HIGHEST BYTE                          |

| 7A                     | FF            | CISTPL_END                            |

| 7C                     | FF            | CISTPL_END                            |

|                        |               |                                       |

|                        |               |                                       |

|                        |               |                                       |

|                        |               |                                       |

|                        |               |                                       |

#### **Command Set Table**

| Command                           | Bus   |       | First | Bus Cycle |       | Second Bus Cycle |       |       |

|-----------------------------------|-------|-------|-------|-----------|-------|------------------|-------|-------|

|                                   | Cycle | Opera | Add   | Data      | Opera | Add              | Data  |       |

|                                   | Req   | -tion | ress  |           | -tion | -ress            |       |       |

| Read Array                        | 1     | Write | DA    | FFFFH     |       |                  |       | 1     |

| Read Identifier Codes             | 3     | Write | DA    | 9090H     | Read  | IA               | IID   | 1,2,3 |

| Read Status Register              | 2     | Write | DA    | 7070H     | Read  | DA               | SRD   | 1,2   |

| Clear Status Register             | 1     | Write | DA    | 5050H     |       |                  |       | 1     |

| Block Erase                       | 2     | Write | BA    | 2020H     | Write | BA               | D0D0H | 1     |

| Program                           | 2     | Write | WA    | 4040H     | Write | WA               | WD    | 1,2   |

| Program (Alternate)               | 2     | Write | WA    | 1010H     | Write | WA               | WD    | 1,2   |

| Block Erase or Program<br>Suspend | 1     | Write | DA    | ВОВОН     |       |                  |       | 1     |

| Block Erase or Program<br>Resume  | 1     | Write | DA    | D0D0H     |       |                  |       | 1     |

| Set Block Lock-Bit                | 2     | Write | BA    | 6060H     | Write | BA               | 0101H | 1     |

| Clear Block Lock-Bit              | 2     | Write | DA    | 6060H     | Write | DA               | D0D0H | 1     |

Table 8

#### Notes:

- 1. DA = A device-level (or device pair) address within the card.

- BA = Address within the block of a specific device (device pair) being erased or locked.

- WA = Address of memory location to be written.

- IA = Identifier address; 00H for manufacture code (8989H). 02H for device code (A6A6H for 28F008S5, AAAAH for 28F016S5). xx0004H for block lock configuration. Where xx represents the block number in the device.  $xx = 00H \sim 0$ FH for 28F008S5,  $xx = 00H \sim 1$ FH for 28F016S5.

- 2. SRD = Data read from Device Status Register.

- WD = Data to be written at location WA. Data is latched on the rising edge of WE\*.

- IID = Data read from identifier codes.

- 3. Following this command, read operations access manufacturer, device code and block lock configuration.

#### **Command Definitions**

When  $V_{PPL}$  is applied to the  $V_{PP1}$ ,  $V_{PP2}$  pins , read operations from the Status Register , intelligent identifiers , or array blocks are enabled. Placing  $V_{PPH1}$  or  $V_{PPH2}$  on  $V_{PP1}$ ,  $V_{PP2}$  pins enables successful block erase, program and lock-bit operations.

Card operations are selected by writing specific commands into the Command User Interface (CUI). Command Set Tables defines this series Flash cards commands.

#### **Read Array Command**

Upon initial card powerup and after exit from deep powerdown mode, this series Flash cards default to the Read Array mode. This operation is also entered by writing FFFFH into the Command User Interface (CUI). Microprocessor read cycles retrieve array data. The card remains enabled for reads until the CUI contents are altered by issuing a valid command. Once the internal Write State Machine (WSM) has started a block-erase, program or lock-bit operation, the card will not recognize the Read Array command until the WSM has completed its operation unless the WSM is suspended via an Erase Suspend or Program Suspend command. The Read Array command functions independently of the  $V_{PP}$  voltage.

#### **Read Identifier Codes Command**

The Read Identifier Codes operation is initiated by writing 9090H into the CUI. Following the command write, read cycles from addresses shown in table below access the manufacturer, device and block lock configuration codes. It remains in this mode until the CUI receives another command. This command functions independently of the  $V_{PP}$  voltage.

| Code              | Word Access |              | Note     |

|-------------------|-------------|--------------|----------|

|                   | Address     | Data         |          |

| Manufacturer ID   | 000000Н     | 8989H        |          |

| Device ID         | 000002H     | A6A6H        | 28F008S5 |

|                   | 000002H     | AAAAH        | 28F016S5 |

| Block Lock        | xx0004H     |              |          |

| Configuration     |             |              |          |

| Block is unlocked |             | D0, D8 = '0' |          |

| Block is locked   |             | D0, D8 = '1' |          |

| Reserved          |             | D1~D7,D9~D15 |          |

Note:  $xx = 00H \sim 0FH$  (block number) in 28F008S5,  $xx = 00H \sim 1FH$  (block number) in 28F016S5.

### **Read Status Register Command**

The 28F008S5 (or 28F016S5) devices on this series card each contains a status register which may be read to determine when a program or block erase operation is complete, and whether that operation completed successfully. The status register may be read at any time by writing the Read Status Register command to the CUI. After writing this command, all subsequent read operations output data from the status register, until the CUI receives another command. The contents of the status register are latched on the falling edge of  $OE^*$ ,  $CE1^*$  (and/or  $CE2^*$ ), whichever occurs first.  $CE1^*$ ,  $CE2^*$  or  $OE^*$  must be toggled to  $V_{IH}$  before further reads to update the status register latch. The Read Status Register command functions independently of the  $V_{PP}$  voltage.

SERIES100FLADS0 11/23 0102V0

### **Clear Status Register Command**

Status register bits SR.5, SR.4, SR.3, SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 10 and its description). By allowing system software to control the resetting of these bits, several operations may be performed (such as cumulatively writing several bytes or erasing or locking multiple blocks in sequence). The Status Register may then be polled to determine if an error occurred during that sequence. This adds flexibility to the way the device may be used.

To clear the Status Register, the Clear Status Register command is written to the CUI. The Clear Status Register command functions independently of the  $V_{PP}$  voltage. This command is not functional during block erase or program suspend modes.

#### **Block Erase Command**

Within a device , erase is performed on one device block at a time , initiated by a two-cycle command sequence. After the system switches  $V_{PP}$  to  $V_{PPH}$  , an Erase Setup command (2020H) prepares the CUI for the Erase Confirm command (D0D0H). The device's WSM controls the erase algorithms internally. After receiving the two-command erase sequence , the device automatically outputs Status Register data when read (See Figure 4). If the command after erase setup is not an Erase Confirm command , the CR sets the Write Failure and Erase Failure bits of the Status Register , places the device into the Read Status Register mode , and waits for another command. The Erase Confirm command enables the WSM for erase (simultaneously closing the address latches for that device's block. The CPU detects the completion of the erase operation by analyzing card-level or device -level indicators. Card-level indicators include the RY/BY\* pin and the READY-BUSY\* Status Register ; while device-level indicators include the specific device's Status Register. Only the Read Status Register command is valid while the erase operation is active. Upon completion of the erase sequence (see section on Status Register) the device's Status Register reflects the result of the erase operation. The device remains in the Read Status Register mode until the CUI receives a new command.

The two-step block-erase sequence ensures that memory contents are not accidentally erased. Erase attempts while  $V_{PPL} < V_{PP} < V_{PPH}$  produce spurious results and are not recommended. Reliable block erasure only occurs when  $V_{PP} = V_{PPH}$ . In the absence of this voltage , memory contents are protected against erasure. If block erase is attempted while  $V_{PP} = V_{PPL}$ , the  $V_{PP}$  Status bit (SR.3) in the Status Register will be set to "1".

When erase completes, the Erase Status bit (SR.5) in the Status Register should be checked. If an erase error is detected, the device's Status Register should be cleared before system software attempts corrective actions. The CUI remains in Read Status Register mode until receiving a new command.

Note :  $V_{PPH}$  can be either  $V_{PPH1}$  (4.5V to 5.5V) or  $V_{PPH2}$  (11.4V to 12.6V)

SERIES100FLADS0 12/23 0102V0

#### **Block Erase Suspend/Block Erase Resume Commands**

Block Erase Suspend command allows block erase interruption in order to read data from or program data to another block of memory. Once the block erase process starts, writing the Block Erase Suspend command to the CUI requests the WSM to suspend the block erase sequence at a predetermined point in the erase algorithm. The device continues to output Status Register data when read, after the Block Erase Suspend command is written to it.

Polling the device's WSM Status bit (SR.7) and Erase Suspend Status bit (SR.6) in the Status Register, or the card's RY/BY\* pin, will determine when the erase operation has been suspended (both bits will be set to '1' and card's RY/BY\* pin will also transition to  $V_{OH}$ ). At this point, a Read Array command can be written to the device's CUI to read data from blocks **other than that which is suspended**. The only other valid commands, at this time, are Read Status Register command and Erase Resume command, at which time the WSM will continue with the block erase process. The WSM Status bit (SR.7) and Erase Suspend Status bit (SR.6) will be cleared to '0' and card's RY/BY\* pin will return to  $V_{OL}$ . After the Block Erase Resume command is written to CUI, the device automatically outputs Status Register data when read. If  $V_{PP}$  goes low during Block Erase Suspend , the  $V_{PP}$  Status bit (SR.3) in the Status Regster is set.

#### **Program Command**

A data-program operation is executed by a two-command sequence. After the system switches  $V_{PP}$  to  $V_{PPH}$ , the write setup command (4040H or 1010H) is written to the CUI, followed by a second write specifying the address and data (latched on the rising edge of WE\*) to be programmed. The device's WSM controls the program and program verify algorithms internally. After receiving the two-command write sequence, the device automatically outputs Status Register data when read. The CPU detects the completion of the program operation by analyzing the WSM Status bit (SR.7) in the Status Register or the output of the RY/BY\* pin of the card. Only the Read Status Register command is valid while the program operation is active. Upon completion of the program operation, the Program Status bit (SR.4) should be checked. If error is detected, the status register should be cleared. The WSM verify only detects errors for '1's that do not program to '0's successfully. The CUI remains in the Read Status Register mode until it receives a new command.

**Note**: VPPH can be either VPPH1 (4.5V to 5.5V) or VPPH2 (11.4V to 12.6V)

SERIES100FLADS0 13/23 0102V0

### **Program Suspend/Program Resume Commands**

The Program Suspend command allows program interruption in order to read data from other memory location. Once the program process starts, writing the Program Suspend command to the CUI requests the WSM to suspend the program sequence at a predetermined point in the program algorithm. The device continues to output Status Register data when read, after the Program Suspend command is written to it.

Polling the device's WSM Status bit (SR.7) and Program Suspend Status bit (SR.2) in the Status Register, or the card's RY/BY\* pin, will determine when the program operation has been suspended (both bits will be set to '1' and card's RY/BY\* pin will also transition to  $V_{OH}$ ). At this point, a Read Array command can be written to the device's CUI to read data from any memory location **other than the suspended location**. The only other valid commands, at this time, are Read Status Register command and Program Resume command, at which time the WSM will continue with the program process. The WSM Status bit (SR.7) and Program Suspend Status bit (SR.2) will be cleared to '0' and card's RY/BY\* pin will return to  $V_{OL}$ . After the Program Resume command is written to CUI, the device automatically outputs Status Register data when read.  $V_{PP}$  MUST remain at  $V_{PPH}$  (the same  $V_{PP}$  voltage level used for program operation) during Program Suspend operation.

Note:  $V_{PPH}$  can be either  $V_{PPH1}$  (4.5V to 5.5V) or  $V_{PPH2}$  (11.4V to 12.6V)

### Set Block Lock-Bit Command, Clear Block Lock-Bit Command

The Set Block Lock-Bit command enables the host to lock individual blocks in the memory array. The block lock-bits gate the program and block erase operations. All set block lock-bits are cleared in parallel by the Clear Block Lock-Bit command. These are a two-cycle command. The host writes the Set Block Lock-Bit setup command along with the appropriate block or device address followed by the Set Block Lock-Bit confirm command (and the address in the block to be locked). The WSM controls the Set Lock-bit algorithm. The host writes the Clear Block Lock-Bit setup command followed by the Clear Block Lock-Bit confirm command. Upon the completion of the command sequence, the device automatically outputs Status Register data when read. Polling the device's WSM Status bit (SR.7) be set to '1' or the card's RY/BY\* pin transition to V<sub>OH</sub>, the host knows the Set Lock-Bit operation or the Clear Lock-Bit operation completed. The host should check Status Register bit (SR.4) for Set Block Lock-Bit command or Status Register bit (SR.5) for Clear Block Lock-Bit command. If an error is detected, the Status Register should be cleared. The CUI remains in the Read Status Register mode until a new command is issued.

SERIES100FLADS0 14/23 0102V0

### **Device Status Register Definition**

Each 28F008S5 (or 28F016S5) device in this series Flash memory card contains a Status Register which displays the condition of its Write State Machine (WSM). The Status Register is read at any time by writing the Read Status command to the CUI. After writing this command, all subsequent Read operations output data from the Status Register, until another valid command is written to the CUI.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WSMS  | ESS   | ECLBS | PSLBS | VPPS  | PSS   | DPS   | R     |

Table 9

#### **Bit 7 (SR.7) --- WSM Status**

'1' = Ready '0' = Busy

Before checking Program or Erase Status bit for success, check this bit first for determining the completion of program, block erase, or lock-bit configuration. SR.6 ~ SR.0 are invalid when SR.7 is '0'.

#### Bit 6 (SR.6) --- Erase Suspend Status

'1' = Block Erase Suspended '0' = Block Erase in Progress/Completed

#### Bit 5 (SR.5) --- Erase and Clear Block Lock-Bits Status

'1' = Error in Block Erase or Clear Block Lock-Bits operation

'0' = Successful Block Erase or Clear Block Lock-Bits operation

#### Bit 4 (SR.4) --- Program and Set Block Lock-Bits Status

'1' = Error in Program or Set Block Lock-Bits operation

'0' = Successful Program or Set Block Lock-Bits operation

#### Bit 3 (SR.3) --- VPP Status

'1' =  $V_{PP}$  voltage low detected, operation abort '0' =  $V_{PP}$  voltage OK

#### Bit 2 (SR.2) --- Program Suspend Status

'1' = Program Suspended '0' = Program in Progress/Completed

#### Bit 1 (SR.1) --- Device Protect Status

'1' = Block Lock-Bit detected, operation abort '0' = Unlock

#### Bit 0 --- Reserved for future enhancements

This bit is reserved for future use and should be masked out when polling the Status Register.

## **Device -- Level Automated Program Algorithm**

Please refer to the 'Automated Program Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

### **Device--Level Automated Block Erase Algorithm**

Please refer to the 'Automated Block Erase Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

### **Device--Level Program Suspend/Resume Algorithm**

Please refer to the 'Program Suspend/Resume Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

## **Device--Level Block Erase Suspend/Resume Algorithm**

Please refer to the 'Block Erase Suspend/Resume Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

### **Device--Level Set Block Lock-Bit Algorithm**

Please refer to the 'Set Block Lock-Bit Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

#### **Device--Level Clear Block Lock-Bit Algorithm**

Please refer to the 'Clear Block Lock-Bit Flowchart' in the INTEL 28F008S5/28F016S5 data sheet.

SERIES100FLADS0 16/23 0102V0

#### **DC** Electrical Characteristics

(recommended operating conditions unless otherwise noted)

| Symbol              | Parameter                                                   | min  | max   | Unit | Test Condition                             |

|---------------------|-------------------------------------------------------------|------|-------|------|--------------------------------------------|

| $I_{LI}$            | Input Leakage Current                                       | -10  | 10    | uA   | $V_{IN} = 0V$ to $V_{CC}$ (Note 1)         |

|                     |                                                             | -70  | 10    | uA   | $V_{IN} = 0V$ to $V_{CC}$ (Note 2)         |

| $I_{LO}$            | Output Leakage Current                                      | -10  | 10    | uA   | $CE1* = CE2* = V_{IH}$ or                  |

|                     |                                                             |      |       |      | $OE* = V_{IH}$ , $V_{OUT} = 0V$            |

|                     |                                                             |      |       |      | to V <sub>CC</sub> (Note 3)                |

| $V_{OH}$            | Output High Voltage                                         | 3.8  |       | V    | $I_{OH} = -2.0 \text{mA} \text{ (Note 4)}$ |

| $V_{OL}$            | Output Low Voltage                                          |      | 0.4   | V    | $I_{OL} = 3.2$ mA (Note 4)                 |

| $I_{CCR}$           | V <sub>CC</sub> Read Current                                |      | 110   | mA   | Min. cycle, I <sub>OUT</sub> = 0mA         |

| $I_{CCW}$           | V <sub>CC</sub> Program/Set Block<br>Lock-Bit Current       |      | 80    | mA   | $V_{PP} = V_{PPH1}$ or $V_{PPH2}$          |

| I <sub>CCE</sub>    | V <sub>CC</sub> Block Erase/Clear<br>Block Lock-Bit Current |      | 70    | mA   | $V_{PP} = V_{PPH1}$ or $V_{PPH2}$          |

| I <sub>CCWS</sub>   | V <sub>CC</sub> Program/Block Erase                         |      | 20    | mA   | Program suspended                          |

| $I_{CCES}$          | Suspend Current                                             |      |       |      | Block Erase suspended                      |

| $I_{CCS}$           | V <sub>CC</sub> Standby Current                             |      | 1.5   | mA   | $CE1* = CE2* = V_{IH}$ or                  |

|                     |                                                             |      |       |      | V <sub>CC</sub> -0.2V                      |

| $I_{PPR}$           | V <sub>PP</sub> Read Current                                |      | 1.0   | mA   | $V_{PP} > V_{CC}$                          |

| $I_{\mathrm{PPW}}$  | V <sub>PP</sub> Program/Set Block                           |      | 80    | mA   | $V_{PP} = 4.5 V \text{ to } 5.5 V$         |

|                     | Lock-Bit Current                                            |      | 30    | mA   | $V_{PP} = 11.4V \text{ to } 12.6V$         |

| $I_{PPE}$           | V <sub>PP</sub> Block Erase/Clear                           |      | 40    | mA   | $V_{PP} = 4.5 \text{V to } 5.5 \text{V}$   |

|                     | Block Lock-Bit Current                                      |      | 15    | mA   | $V_{PP} = 11.4V \text{ to } 12.6V$         |

| $I_{PPWS}$          | V <sub>PP</sub> Program/Block Erase                         |      | 0.4   | mA   | Program/Block Erase                        |

| $I_{PPES}$          | Suspend Current                                             |      |       |      | Suspended                                  |

| $I_{PPS}$           | V <sub>PP</sub> Standby Current                             |      | 40    | uA   | $V_{PP} \leq V_{CC}$                       |

| $V_{PPH1}$          | V <sub>PP</sub> Voltage (Program,<br>Block Erase, Set/Clear | 4.5  | 5.5   | V    |                                            |

|                     | Block Lock-Bit)                                             |      |       |      |                                            |

| $V_{\mathrm{PPH2}}$ | V <sub>PP</sub> Voltage (Program,                           | 11.4 | 12.6  | V    |                                            |

|                     | Block Erase, Set/Clear<br>Block Lock-Bit)                   |      |       |      |                                            |

|                     |                                                             |      | Jo 10 | •    |                                            |

Table 10

Note: 1.) Except CE1\*, CE2\*, WE\*, OE\* pins.

2.) For CE1\* , CE2\* , WE\* , OE\* pins.

3.) Except BVD1\*, BVD2\*, CD1\*, CD2\* pins.

4.) Except CD1\*, CD2\* pins.

SERIES100FLADS0 17/23 0102V0

### **AC Electrical Characteristics**

(recommended operating conditions unless otherwise noted)

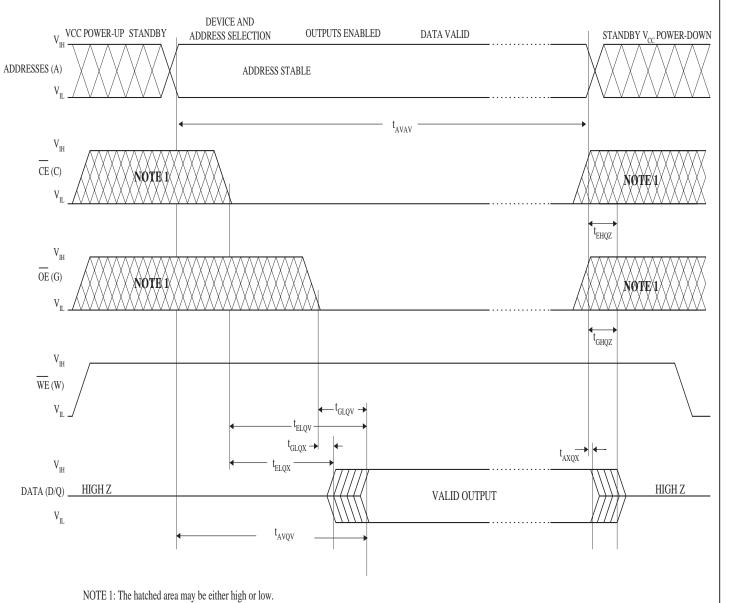

## **Read Cycle**

| Symbol            |                       | Parameter                      | Note | Min | Max | Unit |

|-------------------|-----------------------|--------------------------------|------|-----|-----|------|

| t <sub>AVAV</sub> | $t_{RC}$              | Read Cycle Time                |      | 200 |     | ns   |

| t <sub>AVQV</sub> | t <sub>a</sub> (A)    | Address Access Time            |      |     | 200 | ns   |

| t <sub>ELQV</sub> | t <sub>a</sub> (CE)   | Card Enable Access Time        |      |     | 200 | ns   |

| $t_{GLQV}$        | t <sub>a</sub> (OE)   | Output Enable Access Time      |      |     | 100 | ns   |

| $t_{\rm EHQZ}$    | t <sub>dis</sub> (CE) | Output Disable Time (CE*)      |      |     | 90  | ns   |

| $t_{ m GHQZ}$     | t <sub>dis</sub> (OE) | Output Disable Time (OE*)      |      |     | 90  | ns   |

| $t_{\rm ELQX}$    | t <sub>en</sub> (CE)  | Output Enable Time (CE*)       |      | 5   |     | ns   |

| $t_{GLQX}$        | t <sub>en</sub> (OE)  | Output Enable Time (OE*)       |      | 5   |     | ns   |

| t <sub>AXQX</sub> | $t_{v}(A)$            | Data Valid from Address Change |      | 0   |     | ns   |

Table 11

## Write Cycle

|                    | Symbol                   | Parameter                                      | Min | Typ | Max | Unit |

|--------------------|--------------------------|------------------------------------------------|-----|-----|-----|------|

| $t_{AVAV}$         | t <sub>wc</sub>          | Write Cycle Time                               | 200 |     |     | ns   |

| t <sub>WLWH</sub>  | t <sub>w</sub> (WE)      | Write Pulse Width                              | 100 |     |     | ns   |

| $t_{ m AVWL}$      | t <sub>su</sub> (A)      | Address Setup Time                             | 10  |     |     | ns   |

| t <sub>AVWH</sub>  | t <sub>su</sub> (A-WEH)  | Address Setup Time for WE*                     | 140 |     |     | ns   |

| t <sub>VPWH</sub>  | t <sub>vps</sub>         | V <sub>PP</sub> Setup to WE* Going High        | 100 |     |     | ns   |

| t <sub>ELWH</sub>  | t <sub>su</sub> (CE-WEH) | Card Enable Setup Time for WE*                 | 140 |     |     | ns   |

| $t_{\rm DVWH}$     | t <sub>su</sub> (D-WEH)  | Data Setup Time for WE*                        | 60  |     |     | ns   |

| t <sub>WHDX</sub>  | t <sub>h</sub> (D)       | Data Hold Time                                 | 30  |     |     | ns   |

| t <sub>WHAX</sub>  | t <sub>rec</sub> (WE)    | Write Recover Time                             | 30  |     |     | ns   |

| t <sub>WHRL</sub>  |                          | WE High to RY/BY*                              |     |     | 120 | ns   |

| t <sub>WHRH1</sub> |                          | Program Time (5V V <sub>PP</sub> )             | 6.5 | 8   |     | us   |

|                    |                          | Program Time (12V V <sub>PP</sub> )            | 4.8 | 6   |     | us   |

| t <sub>WHRH2</sub> |                          | Block Erase Time (5V V <sub>PP</sub> )         | 0.9 | 1.1 |     | sec  |

|                    |                          | Block Erase Time (12V V <sub>PP</sub> )        | 0.3 | 1.0 |     | sec  |

| t <sub>WHRH3</sub> |                          | Set Block Lock-Bit Time (5V V <sub>PP</sub> )  | 9.5 | 12  |     | us   |

|                    |                          | Set Block Lock-Bit Time (12V V <sub>PP</sub> ) | 7.8 | 10  |     | us   |

| t <sub>WHRH4</sub> |                          | Clear Block Lock-Bit (5V V <sub>PP</sub> )     | 0.9 | 1.1 |     | sec  |

|                    |                          | Clear Block Lock-Bit (12V V <sub>PP</sub> )    | 0.3 | 1.0 |     | sec  |

| t <sub>WHGL</sub>  | t <sub>h</sub> (OE-WE)   | Write Recovery before Read                     | 10  |     |     | ns   |

Table 12

## Write Cycle (CE\* controlled)

|                    | Symbol                   | Parameter                                      | Min | Тур | Max | Unit |

|--------------------|--------------------------|------------------------------------------------|-----|-----|-----|------|

| t <sub>AVAV</sub>  | $t_{\rm wc}$             | Write Cycle Time                               | 200 |     |     | ns   |

| t <sub>ELEH</sub>  | t <sub>w</sub> (WE)      | Card Enable Pulse Width                        | 120 |     |     | ns   |

| t <sub>AVEL</sub>  | t <sub>su</sub> (A)      | Address Setup Time                             | 20  |     |     | ns   |

| t <sub>AVEH</sub>  | t <sub>su</sub> (A-WEH)  | Address Setup Time for CE*                     | 140 |     |     | ns   |

| t <sub>VPEH</sub>  | $t_{ m vps}$             | VPP Setup to CE* Going High                    | 100 |     |     | ns   |

| t <sub>WLEH</sub>  | t <sub>su</sub> (CE-WEH) | Write Enable Setup Time for CE*                | 140 |     |     | ns   |

| $t_{DVEH}$         | t <sub>su</sub> (D-WEH)  | Data Setup Time for CE*                        | 60  |     |     | ns   |

| $t_{EHDX}$         | t <sub>h</sub> (D)       | Data Hold Time                                 | 30  |     |     | ns   |

| $t_{EHAX}$         | t <sub>rec</sub> (WE)    | Write Recover Time                             | 30  |     |     | ns   |

| t <sub>EHRL</sub>  |                          | CE* High to RY/BY*                             |     |     | 120 | ns   |

| t <sub>EHRH1</sub> |                          | Program Time (5V V <sub>PP</sub> )             | 6.5 | 8   |     | us   |

|                    |                          | Program Time (12V V <sub>PP</sub> )            | 4.8 | 6   |     | us   |

| t <sub>EHRH2</sub> |                          | Block Erase Time (5V V <sub>PP</sub> )         | 0.9 | 1.1 |     | sec  |

|                    |                          | Block Erase Time (12V V <sub>PP</sub> )        | 0.3 | 1.0 |     | sec  |

| t <sub>EHRH3</sub> |                          | Set Block Lock-Bit Time (5V V <sub>PP</sub> )  | 9.5 | 12  |     | us   |

|                    |                          | Set Block Lock-Bit Time (12V V <sub>PP</sub> ) | 7.8 | 10  |     | us   |

| t <sub>EHRH4</sub> |                          | Clear Block Lock-Bit (5V V <sub>PP</sub> )     | 0.9 | 1.1 |     | sec  |

|                    |                          | Clear Block Lock-Bit (12V V <sub>PP</sub> )    | 0.3 | 1.0 |     | sec  |

| t <sub>EHGL</sub>  | t <sub>h</sub> (OE-WE)   | Write Recovery before Read                     | 10  |     |     | ns   |

Table 13

## **Read Cycle Timing Diagram**

Figure 3

## **Write Cycle Timing Diagram**

## $Write\ Cycle\ Timing\ Diagram\ (CE*\ controlled)$

## **Outline Dimensions (Unit: mm)**

FLASH CARD (Write Protect)